Our Courses

Course 101 Machine Learning For Internet of Things – IoT

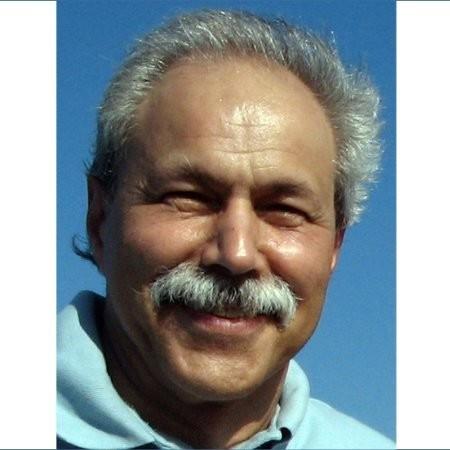

Dr. Rikard König, PhD, co-founder and Chief Data Scientist at Ekkono Solutions, and Senior Lecture

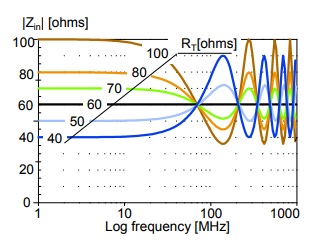

Course 007 Behavioral Modeling and Digital Predistortion of RF Power Amplifiers

Dr John Wood, Owner and Technical Consultant, Obsidian Microwave, LLC, USA is teaching this 3-day co

Course 008 Advanced RF Power Amplifier Techniques for Modern Wireless and Microwave Systems

Dr. Steve C. Cripps University of Cardiff and Hywave Associates, UK, Dr. Jeff Powell, Skyarna Ltd, U

Course 011 Digital Signal Analysis Techniques: Time, Frequency, and Spatial Algorithms

Professor Gonzalo Seco-Granados and Professor José A. López-Salcedo are teaching this 3-day course

Course 013 Digital Imaging: Image Capturing, Image Sensors - Technologies and Applications

Professor Albert J.P Theuwissen, Delft University of Technology, the Netherlands and Harvest Imaging

Course 014 Digital Camera Systems

Professor Albert J.P Theuwissen, Delft University of Technology, the Netherlands and Harvest Imaging

Course 015 RF Design and Simulation of Wireless Systems

Dr. Rowan Gilmore, Adjunct Professor, University of Queensland, and CEO EM Solutions Pty Ltd., Austr

Course 016 Versatile Video Coding: Algorithms and Specification

Dr. Mathias Wien, RWTH Aachen University, Germany, is teaching about Versatile Video Coding.

Video

Course 063 Optical Sensors: Photodetector, Low Noise Interfacing, Signal Conditioning and ASIC Integration

Dr. Farzad Parsaie, founder of SAND Microsystems GmbH, Switzerland is teaching this 2-day course in

Course 064 LiDAR Sensors from System to Transistor/Device Level and Miniaturization through ASIC and (Co-)Packaging

Dr. Farzad Parsaie, founder of SAND Microsystems GmbH, Switzerland is teaching this 5-day course on

Course 401 Industrial Failure and Root Cause Investigation - for Management

Mrs. Elisabet Blom, MSc, Vibration Specialist and Owner, Tremula Teknologi AB, Sweden.

A failure

Course 402 Industrial Failure and Root Cause Investigation - Technology Focus

Mrs. Elisabet Blom , MSc, Vibration Specialist and Owner, Tremula Teknologi AB, Sweden.

Failure

Course 870 Invention and Innovation – Creation and Management of World Class Patents

Dr. Walter Lange, is teaching this two-day class focusing on the fundamentals to enable successful

Course 201 Blockchain Technology: Programmable Scarcity

Mr. Jonatan Bergquist, consultant at Datarella, Munich, Germany, is teaching this 2-day course about

Course 202 Venture Capital

Ms. Ekaterina (Katya) Dorozkhina, Co-founding Partner and CEO of Starta Ventures, is teaching this

Course 203 Blockchain - Reshaping the World

Mr. Per Håkansson, Managing Editor of Inside Blockchain, TEDx speaker, Learning facilitator, from

Course 007 Behavioral Modeling and Digital Predistortion of RF Power Amplifiers

Dr John Wood, Owner and Technical Consultant, Obsidian Microwave, LLC, USA is teaching this 3-day co

Course 008 Advanced RF Power Amplifier Techniques for Modern Wireless and Microwave Systems

Dr. Steve C. Cripps University of Cardiff and Hywave Associates, UK, Dr. Jeff Powell, Skyarna Ltd, U

Course 015 RF Design and Simulation of Wireless Systems

Dr. Rowan Gilmore, Adjunct Professor, University of Queensland, and CEO EM Solutions Pty Ltd., Austr

Course 019 RF and Microwave Circuit Design: Applications and Theory

Dr. Rowan Gilmore, Adjunct Professor, University of Queensland, and CEO of EM Solutions Pty Ltd., Au

Course 025 Hands On Software Defined Radio

Dr. Richard G. Ranson, Consultant at Radio System Design, UK, is teaching this course in Radio Commu

Course 026 Essentials of Radio Communications Systems

Dr. Richard G. Ranson, Consultant at Radio System Design, UK, is teaching this 2-day course in Radio

Course 030 PCB Filters and Multiplexers using Standard SMT Components

Mr. Daniel G. Swanson Jr., DGS Associates, LLC, Boulder, CO. USA, is teaching this course in PCB Fi

Course 030-031 - Bundle PCB Filters and Multiplexers

Daniel G. Swanson Jr., DGS Associates, LLC, Boulder, CO. USA, is teaching this bundle of two courses

Course 089 Plasma Etching for Microelectronics Applications - ECourse

Dr. Maxime Darnon, LN2/CNRS, Sherbrooke, Canada, is teaching this short Ecourse in Plasma Etching f

Course 090 Plasma Etching for Microelectronics Applications: From Fundamental to Practical Applications - ECourse

Dr. Maxime Darnon, LN2/CNRS, Sherbrooke, Canada, is teaching this Ecourse in Plasma Etching for Mi

Course 607 Angular Development

Angular is a modern, performance-efficient and powerful single-page frontend framework.

It is an o

Course 701 Battery Storage Technology: Opportunities and Uses - eCourse

Achieving the European goals by 2030 is an exciting but challenging goal. A critical piece of the pu

Course 702 Battery Storage Basics - eCourse

Batteries are the fastest growing storage technology and a key enabler of a low-carbon economy. The

Course 703 Energy Systems Integration: the Future of Transport - eCourse

The transportation sector is at a crossroads. As one of the biggest consumers of the world’s energ

Course 704 Introduction to Solid-State Batteries - eCourse

As the industry is pursuing ever-higher energy density, faster charging and lower cost, the current

Course 705 Managing Energy Data: Advanced Analytics- eCourse

The Internet of Things (IoT) revolution (e.g., the vast spread of smart meters worldwide) is generat

Course 301 Linux Embedded Development

Mr. Kjell Enblom Senior Consultant at MindRoad AB, Sweden is teaching this 2-day course. Learn a s

Course 302 Unix Scripting and Shell Programming

Mr. Kjell Enblom, Senior Consultant at MindRoad AB, Sweden is teaching this 2-day course about Uni

Course 303 Embedded Development in Yocto

Mr. Kjell Enblom, Senior Consultant at MindRoad AB, Sweden teaching this 2-day course. Learn how to�

Course 304 The Diameter Protocol for AAA in LTE

Mr. Anders Larsson, PhD in Computer Science from Linköping University, Sweden is teaching this 2-da

Course 305 Linux Driver Development

Mr. Kjell Enblom, Senior Consultant at MindRoad AB, Sweden is teaching this 2-day course on how to b

Course 306 FPGA Development

Mr. Anders Larsson, PhD in Computer Science from Linköping University, Sweden is teaching this 3-da

Course 053 Mastering Power Integrity with Signal Integrity and EMC Foundations

Dr. István Novák, Principal Signal and Power Integrity Engineer, Samtec, Boston, USA, is teaching

Course 054 Signal and Power Integrity: Advanced High-Speed Design and Characterization

Dr. István Novák, Principal Signal and Power Integrity Engineer, Samtec, Boston, USA, is teaching

Course 055 Signal Integrity: Advanced High-Speed Design and Characterization

Dr. István Novák, Principal Signal and Power Integrity Engineer, Samtec, Boston, USA, is teaching

Course 056 Power Integrity: Advanced Design and Characterization

Dr. István Novák, Principal Signal and Power Integrity Engineer, Samtec, Boston, USA, is teaching

Course 060 Grounding and Shielding: The Essence of EMC Design

Elya B. Joffe, Electromagnetic Solutions Ltd., Israel is teaching this 4-day course in Advanced EMC

Course 070 High-Speed PCB Design for EMC and Signal Integrity

Mr. Elya B. Joffe, Electromagnetic Solutions Ltd., Israel, is teaching this 5-day advanced design co

Course 071 Transients and Electrical Overstress Protection in Electronic Systems

Mr. Elya B. Joffe, Electromagnetic Solutions Ltd., Israel, is teaching this 3-day course about Trans

Course 812 Practical Antenna Design for Wireless Products

Mr. Henry Lau, CEO of Lexiwave Technology, Hong Kong and US, is teaching this 2-day course on Anten

Course 101 Machine Learning For Internet of Things – IoT

Dr. Rikard König, PhD, co-founder and Chief Data Scientist at Ekkono Solutions, and Senior Lecture

Course 084 Wireless Connectivity for the IoT

Dr. Lutz Konstroffer, RF Consult GmbH, Germany is teaching this 5-day course in Wireless connect

Course 101-102 Machine Learning and IoT

Machine Learning helps connected things to automatically learn its normal state and behavior, which

Course 102 Internet of Things – The Next Big Disruption

Mr. Jon Lindén, CEO at Ekkono Solutions, Sweden, is teaching this two-day course about Internet of

Course 103 Internet of Things for Smart Cities

Mr. Charalampos Stergiopoulos, MSc in Data Communications Systems, is teaching this 3-day course inc

Course 104 Managing CyberSecurity - Awareness by Experience

This 1-day course in Industrial Cyber Security teaches theory and hands-on training by competing in

Course 105 Advanced Industrial CyberSecurity in Practice

Mr. Roland Sako, Security Researcher, ICS CERT, Kaspersky Lab, Switzerland, is teaching this 2-day

Course 106 Rapid IoT Development

Mr. Joshua Hohendorf, Technical Trainer at Telit IoT Platform, Florida, United States, teaches this

Course 401 Industrial Failure and Root Cause Investigation - for Management

Mrs. Elisabet Blom, MSc, Vibration Specialist and Owner, Tremula Teknologi AB, Sweden.

A failure

Course 402 Industrial Failure and Root Cause Investigation - Technology Focus

Mrs. Elisabet Blom , MSc, Vibration Specialist and Owner, Tremula Teknologi AB, Sweden.

Failure

Course 870 Invention and Innovation – Creation and Management of World Class Patents

Dr. Walter Lange, is teaching this two-day class focusing on the fundamentals to enable successful

Course 035 Introduction to Semiconductor Packaging Technology

Dr. Jeff Gambino, ON Semiconductor, United States, is teaching this advanced 3-day course, which wil

Course 036 Silicon Device Technology: Materials and Processing Overview

Dr. Jeffrey Gambino, ON Semiconductor, United States, is teaching this advanced 5-day course, which

Course 037 Power Semiconductor Device Technology

Dr. Jeffrey Gambino, ON Semiconductor, United States, is teaching this advanced 3-day course, which

Course 038 Silicon-on-Insulator Technologies from Microelectronics to MEMS

Professor Jean-Pierre Raskin is teaching this 3-day SEMI course. He will demonstrate the advantages

Course 051 Thin Film Deposition at the Nanoscale: Mechanisms and Applications

Thin Film Technology is pervasive in many applications, including microelectronics, optics, magnetic

Course 057 Synchronization and Interconnect in Multiple Clock Domain Systems-on-Chips, SoCs

Dr. Reuven Dobkin, CTO of vSync Circuits Ltd. is teaching this 4-day course that explains the Scie

Course 061 IC Reliability, Fault Isolation, and Failure Analysis

Mr. David Vallett, PeakSource Analytical, USA, and Dr. Kristof Croes, Group Leader Interconnect Reli

Course 063 Optical Sensors: Photodetector, Low Noise Interfacing, Signal Conditioning and ASIC Integration

Dr. Farzad Parsaie, founder of SAND Microsystems GmbH, Switzerland is teaching this 2-day course in

Course 013 Digital Imaging: Image Capturing, Image Sensors - Technologies and Applications

Professor Albert J.P Theuwissen, Delft University of Technology, the Netherlands and Harvest Imaging

Course 014 Digital Camera Systems

Professor Albert J.P Theuwissen, Delft University of Technology, the Netherlands and Harvest Imaging

Course 016 Versatile Video Coding: Algorithms and Specification

Dr. Mathias Wien, RWTH Aachen University, Germany, is teaching about Versatile Video Coding.

Video

Course 020 Advanced Course on Image Sensor Technology

Professor Albert J.P Theuwissen, Delft University of Technology, the Netherlands and Harvest Imaging

Course 063 Optical Sensors: Photodetector, Low Noise Interfacing, Signal Conditioning and ASIC Integration

Dr. Farzad Parsaie, founder of SAND Microsystems GmbH, Switzerland is teaching this 2-day course in

Course 064 LiDAR Sensors from System to Transistor/Device Level and Miniaturization through ASIC and (Co-)Packaging

Dr. Farzad Parsaie, founder of SAND Microsystems GmbH, Switzerland is teaching this 5-day course on

Course 600 Practical Implementation/Performance of Noise Measurements on a CMOS Image Sensor

Professor Albert J.P. Theuwissen, Delft University of Technology, the Netherlands, Harvest Imaging,

Course 825 Fundamentals of Magnetic-Resonance Imaging (MRI)

Dr. Abbas Omar, University of Magdeburg in Germany, is teaching this 5-day course on Magnetic-Reson

Course 011 Digital Signal Analysis Techniques: Time, Frequency, and Spatial Algorithms

Professor Gonzalo Seco-Granados and Professor José A. López-Salcedo are teaching this 3-day course

Course 016 Versatile Video Coding: Algorithms and Specification

Dr. Mathias Wien, RWTH Aachen University, Germany, is teaching about Versatile Video Coding.

Video

Course 023 Satellite Communication Systems

Professor Michel Bousquet is teaching this 5-day course in Satellite Communication Systems.

Satell

Course 030 PCB Filters and Multiplexers using Standard SMT Components

Mr. Daniel G. Swanson Jr., DGS Associates, LLC, Boulder, CO. USA, is teaching this course in PCB Fi

Course 031 High Q Cavity Filters and Multiplexers

Mr. Daniel G. Swanson Jr., DGS Associates, LLC, Boulder, CO. USA, is teaching this 3-day course in�

Course 032 Planar Filters and Multiplexers

Daniel G. Swanson Jr., DGS Associates, LLC, Boulder, CO. USA, is teaching this 3-day course in Plan

Course 044 Radio Spectrum Management

Mr Olov Carlsson, Senior Director – EM Solutions at Altair Engineering, Sweden is teaching this 3-

Course 047 Neuroscience & QC in Complex Networks

Research Professor Savo Glisic, Worcester Polytechnic Institute, MA, United States, is teaching this

Course 308 Angular - Basic to Expert

Mr. Franz Inselkammer and Mr. Raul Clemente, at Inovum IT Solutions. Barcelona, Spain are teaching t

Course 607 Angular Development

Angular is a modern, performance-efficient and powerful single-page frontend framework.

It is an o

e-Course Bundle 607-609 Angular Development

Angular is a modern, performance-efficient and powerful single-page frontend framework.

It is an o

Course 007 Behavioral Modeling and Digital Predistortion of RF Power Amplifiers

Dr John Wood, Owner and Technical Consultant, Obsidian Microwave, LLC, USA is teaching this 3-day co

Course 008 Advanced RF Power Amplifier Techniques for Modern Wireless and Microwave Systems

Dr. Steve C. Cripps University of Cardiff and Hywave Associates, UK, Dr. Jeff Powell, Skyarna Ltd, U

Course 015 RF Design and Simulation of Wireless Systems

Dr. Rowan Gilmore, Adjunct Professor, University of Queensland, and CEO EM Solutions Pty Ltd., Austr

Course 019 RF and Microwave Circuit Design: Applications and Theory

Dr. Rowan Gilmore, Adjunct Professor, University of Queensland, and CEO of EM Solutions Pty Ltd., Au

Course 025 Hands On Software Defined Radio

Dr. Richard G. Ranson, Consultant at Radio System Design, UK, is teaching this course in Radio Commu

Course 026 Essentials of Radio Communications Systems

Dr. Richard G. Ranson, Consultant at Radio System Design, UK, is teaching this 2-day course in Radio

Course 030 PCB Filters and Multiplexers using Standard SMT Components

Mr. Daniel G. Swanson Jr., DGS Associates, LLC, Boulder, CO. USA, is teaching this course in PCB Fi

Course 031 High Q Cavity Filters and Multiplexers

Mr. Daniel G. Swanson Jr., DGS Associates, LLC, Boulder, CO. USA, is teaching this 3-day course in�

Course 047 Neuroscience & QC in Complex Networks

Research Professor Savo Glisic, Worcester Polytechnic Institute, MA, United States, is teaching this

Course 048 QC in Chemistry & Biology - Complex Networks

Research Professor Savo Glisic, Worcester Polytechnic Institute, MA, United States, is teaching this

Course 049 Quantum vs Postquantum Cryptography

Research Professor Savo Glisic, Worcester Polytechnic Institute, MA, United States, is teaching this

Course 078 Quantum Computing and QC-Assisted Communications

Professor Savo Glisic, Worcester Polytechnic Institute, MA, United States, is teaching this 3-day

Course 079 Future Wireless Networks: 5G/6G Technology

Research Professor Savo Glisic, Worcester Polytechnic Institute, MA, United States, is teaching thi

Course 080 Artificial Intelligence in Wireless Networks

Research Professor Savo Glisic, Worcester Polytechnic Institute, MA, United States, is teaching this

Course 860 Bluetooth Low Energy – Technology, Trends and Applications

Mr. Naresh Gupta, Author – Inside Bluetooth Low Energy, is the instructor for this 5-day course in

Course 501 Know, Read & Understand Your Piping & Instrumentation Diagrams (P&ID’s)

Mr. Wissem Bouaita, IFP School and Chimie ParisTech, France, is teaching this 2½-day course in Pip

Course 502 Understanding Process Control Used in Process Industries

Mr. Wissem Bouaita, IFP School and Chimie ParisTech, France, is teaching this 2-day course in Proce

Course 503 Flow of Fluids Through Piping Systems

Mr. Wissem Bouaita, IFP School and Chimie ParisTech, France, is teaching this 2-day course in flow o

Course 870 Invention and Innovation – Creation and Management of World Class Patents

Dr. Walter Lange, is teaching this two-day class focusing on the fundamentals to enable successful

Course 023 Satellite Communication Systems

Professor Michel Bousquet is teaching this 5-day course in Satellite Communication Systems.

Satell

Course 820 LEO, MEO and GSO System and Service Integration-Introduction

Mr. Geoff Varrall, Executive Director of RTT Programmes, UK, is teaching this 5-day course.

This co

Course 701 Battery Storage Technology: Opportunities and Uses - eCourse

Achieving the European goals by 2030 is an exciting but challenging goal. A critical piece of the pu

Course 702 Battery Storage Basics - eCourse

Batteries are the fastest growing storage technology and a key enabler of a low-carbon economy. The

Course 703 Energy Systems Integration: the Future of Transport - eCourse

The transportation sector is at a crossroads. As one of the biggest consumers of the world’s energ

Course 704 Introduction to Solid-State Batteries - eCourse

As the industry is pursuing ever-higher energy density, faster charging and lower cost, the current

Course 705 Managing Energy Data: Advanced Analytics- eCourse

The Internet of Things (IoT) revolution (e.g., the vast spread of smart meters worldwide) is generat

Course 870 Invention and Innovation – Creation and Management of World Class Patents

Dr. Walter Lange, is teaching this two-day class focusing on the fundamentals to enable successful

70

Courses

34000

Members

12

topics

7

locations

Popular Courses

Subscribe for a newsletter

Select the technical category of your interest! By signing up to our Newsletter, you will allow us to send you relevant course information. In compliance with GDPR, your email address will not be used in any other way.

Copyright © 2017 CEI-BETA, Inc. All rights reserved.